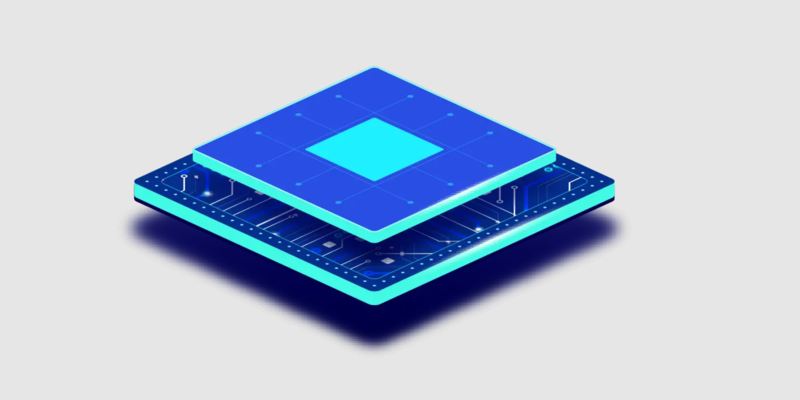

InCore’s core-hubs are comprehensive designs to target all aspects of embedded computing. Core-Hubs are ready to integrate complete CPU complexes that combine multiple, heterogenous cores from various InCore series of cores and combine those with an optimized SoC fabric and extensions

Overview

- Cores – Our fully customizable RISC-V core are designed to meet the specific needs of our customers, with flexible and scalable options that allow for easy customization.

- Azurite, Calcite & Dolomite series of core-hubs are our current baseline architectures, and they cover the breadth of most major application spaces

- Fabric – Our interconnect fabrics provide efficient and reliable communication between different processing units, memory, and peripherals, while our components enable the development of high-performance, low-power, and cost-effective SoCs

- Multiple communication protocols supported within a die – APB, AHB, AXI4, ACE, Tile Link

- Between dies and packages – UCIe, HBM, CXL Gen 3, PCIe

- Multiple NOC topologies – Tree, Mesh (2-D and 3-D), Ring, Bus, Crossbar, SMP support

- UnCore – All Core-Hubs are bundled with conventional RISC-V UnCore components like Platform Interrupt Controllers, Debug, Trace etc. and can be customized by the User.

- Sleep Modes + Debug + TRACE + PLIC + CLINT + CLIC + Customization

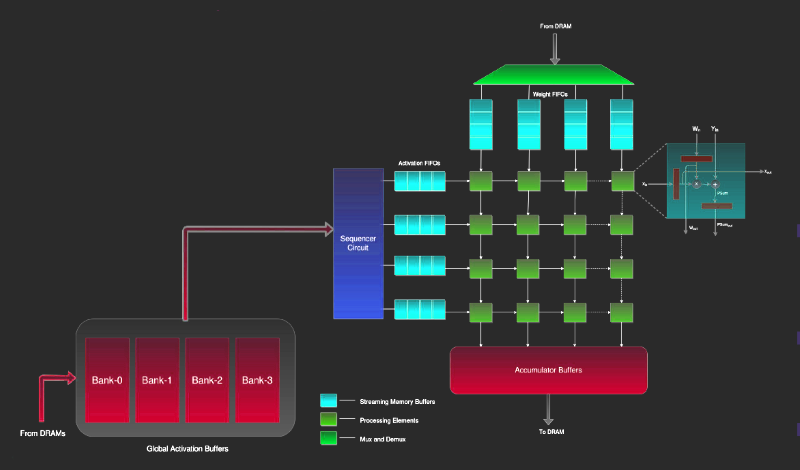

- Accelerators – Our accelerators are designed to boost the performance and security of embedded systems, while minimizing power consumption.

- Cryptographic – Isolated security sub-system, Secure boot, Tamper, Secure memory, Hardware encryption, Side channel resistance, Enhanced security compartments, Secure key storage, EFUSE, OTBN, sPMP/ioPMP, TRNG/PRNG

- AI/ML – Vector, Matrix multiplication

- Vision accelerators – ISP, Computer vision processor

- Other specialised accelerators – DSP, Bit Manip, Video codec (H.265)

RISC-V Baseline core architectures

| Processor Series | Stages | Instruction Issue | Multi-cor Capable | Operating system | Segment |

|---|---|---|---|---|---|

| Azurite | 2+ RV-32 bit | 1 | No | RTOS | Deeply embedded |

| Calcite | 5+ RV-32/64 bit | 1 | Yes | Linux | Embedded & Industrial |

| Dolomite | 8+ RV-64 bit | 1 | Yes | Linux / Android / WearOS | Application & Industrial |

Azurite series

- An extremely efficient implementation for very low area and power. Replace your traditional 8-bit and 32-bit applications such as Sensor Fusion, Wearables, Motor Control, smart IoT and Analog Mixed Signal with Azurite

Calcite series

- An embedded processor providing a optimal balance of area, power and performance; capable of supporting full-featured operating systems such as Linux. Calcite is ideal for networking apps, point-of-sale terminals, AR, VR, IP cameras.

- Multi core variants are available in Calcite

Dolomite series (Releasing end of 2024)

- A wider-issue and throughput enhanced in-order processor to provide maximum single-thread performance. Suitable for mobile devices, storage, high-performance embedded devices

- Multi-threaded and multi-core variants are available in Dolomite

Azurite Core-hub

Targeted for the deeply embedded segment

Key features:

- An in-order 2-stage 64/32-bit processor supporting the latest subset of the ISA.

- Single issue

- Targets mid-range compute systems: 150-300 MHz.

- Variants for low-power and resource constrained applications

Specifications:

- Supports RISC-V ISA: RV[64|32]IMACUBP.

- Supports the OpenOCD based debug environment through JTAG. Non-invasive Debug architecture and Trigger support.

- Non-Coherent Multi-core (heterogenous) support available.

- Support for Resumable NMIs

- Support for Performance Counters

- Caches: upto 32KB blocking Instruction and Data caches.

- Simple operand Bypass.

- Custom CSR Support with daisy chain scheme.

- Instruction Trace support

- PMP Support

- Positioned against ARM’s Cortex Mx

InCore's Azurite Core Generator fuels innovation tailored to diverse applications in the deeply embeeded segments from IoT devices to mini wearables to smart cards. Azurite core-hubs are an extremely efficient implementation for very low area and power. Replace your traditional 8-bit and 32-bit applications with core-hubs from this Azurite core-generator.

Calcite Core-hub

Key features:

- Single issue

- Targets mid-range compute systems: 500-800MHz.

- Supports RISC-V Linux, secure L4

- Variants for low-power and high-performance.

- Positioned against ARM’s Cortex A35

Specifications:

- Supports RISC-V ISA: RV[64|32]IMAFDCSU [HBP].

- Compatible with latest privilege spec (v1.21) of RISC-V ISA and supports the sv32/39/48/57 virtualization scheme.

- MMU and PMP support.

- Single and Double Precision Floating point units compliant with IEEE-754.

- Supports the OpenOCD based debug environment through JTAG. Non-invasive Debug architecture.

- Includes a High performance branch predictor with a Return-Address-Stack.

- Caches: 16KB blocking pipelined Instruction and Data caches.

- Simple Scoreboard for operand Bypass.

- Custom CSR Support with daisy chain scheme.

InCore's Calcite Core Generator fuels innovation tailored to diverse applications in the embeeded and industrial segments from POS terminals to IP cameras. Calcite core-hubs are embedded processors providing an optimal balance of area, power and performance; capable of supporting full-featured operating systems such as Linux.

Dolomite core-hub

Key features:

- Dual issue

- Multiple- ALUs to reduce load-to-use latencies

- Targets mid-range compute systems: 800MHz – 1.5GHz.

- Supports RISC-V Linux, secure L4

- Positioned against ARM’s Cortex A55

Specifications:

- Supports RISC-V ISA: RV[64|32]IMAFDCSU [HBP].

- Compatible with latest privilege spec (v1.21) of RISC-V ISA and supports the sv39/48 virtualization scheme.

- MMU and PMP support.

- Single and Double Precision Floating point units compliant with IEEE-754.

- Supports the OpenOCD based debug environment through JTAG. Non-invasive Debug architecture.

- Includes a High performance branch predictor with a Return-Address-Stack.

- Caches: 16KB blocking pipelined Instruction and Data caches.

- Simple Scoreboard for operand Bypass.

- Custom CSR Support with daisy chain scheme.

- Instruction Trace Support

Dolomite core-hubs are wider-issue and throughput enhanced in-order processors to provide maximum single-thread performance. Suitable for mobile devices, storage, high-performance embedded devices

Resources

sales enquiry